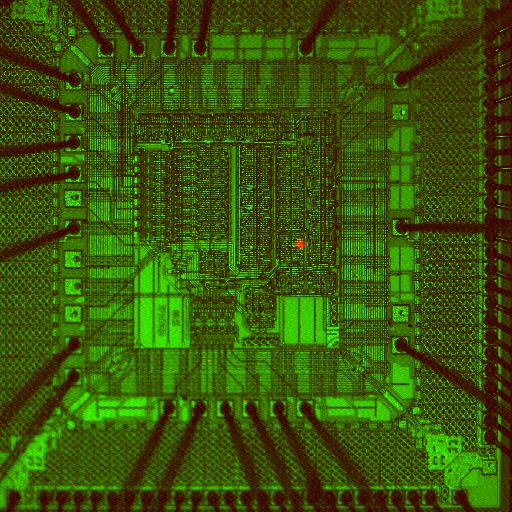

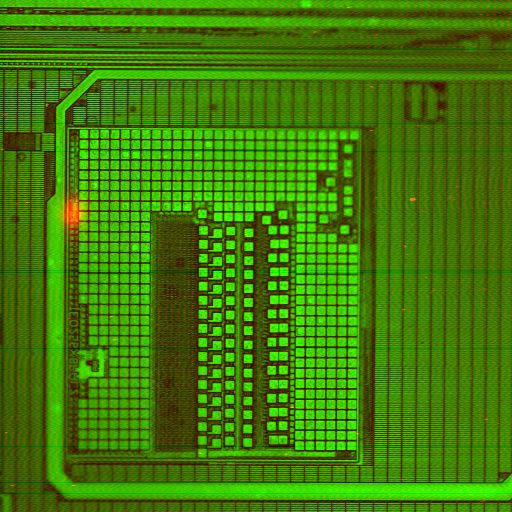

ESD & Latch-up Testing

Electrostatic Discharge (ESD) and latch-up immunity are vital to the reliability of microelectronic products. With more than 20 years relevant experience, LabTest Analytics characterizes the electrostatic and latch-up features of integrated circuits (ICs) for both commercial and military purposes. In the event of ESD or latch-up failure, LabTest Analytics’ analytical staff are on-site and can quickly determine the root cause, saving valuable test time. ESD can severely damage or destroy ICs, therefore specified levels of ESD protection must be demonstrated as part of most product qualifications. LabTest Analytics tests devices to any commercial or military ESD standard and performs curve tracing before and after testing to check for any device changes. LabTest Analytics can also identify weak points in a functioning ESD design, thus enabling future designs to be improved. Latch-up is the creation of a disruptive low-impedance current path between power supply rails, triggered by a parasitic four-layer bipolar structure in CMOS devices.

Equipment and Capabilities

- ESD simulation

- MIL-STD 883

- JEDEC JESD22A114-B/115-A

- TIA/EIA-455-129

FOTP-129 - Human Body Model (HBM) to 8000V

- Machine Model (MM) to 2000V

- Socketed Charged Device Model (SCDM) to 1500V

- Pin counts up to 256 with expandability

- Support for DIP, PLCC, BGA, PGA, QFP, SOIC and CTAB package types

Typical applications

- Reliability analysis

- Failure analysis

- Product ESD qualification

Ultra-Test International Multi-Trace tester

- JEDEC JESD78

- Pin counts up to 625 with expandability

- Support for DIP, PLCC, BGA, PGA, QFP, CTAB package types